7.8: Example Circuits and Netlists

- Page ID

- 2085

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\( \newcommand{\dsum}{\displaystyle\sum\limits} \)

\( \newcommand{\dint}{\displaystyle\int\limits} \)

\( \newcommand{\dlim}{\displaystyle\lim\limits} \)

\( \newcommand{\id}{\mathrm{id}}\) \( \newcommand{\Span}{\mathrm{span}}\)

( \newcommand{\kernel}{\mathrm{null}\,}\) \( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\) \( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\) \( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\id}{\mathrm{id}}\)

\( \newcommand{\Span}{\mathrm{span}}\)

\( \newcommand{\kernel}{\mathrm{null}\,}\)

\( \newcommand{\range}{\mathrm{range}\,}\)

\( \newcommand{\RealPart}{\mathrm{Re}}\)

\( \newcommand{\ImaginaryPart}{\mathrm{Im}}\)

\( \newcommand{\Argument}{\mathrm{Arg}}\)

\( \newcommand{\norm}[1]{\| #1 \|}\)

\( \newcommand{\inner}[2]{\langle #1, #2 \rangle}\)

\( \newcommand{\Span}{\mathrm{span}}\) \( \newcommand{\AA}{\unicode[.8,0]{x212B}}\)

\( \newcommand{\vectorA}[1]{\vec{#1}} % arrow\)

\( \newcommand{\vectorAt}[1]{\vec{\text{#1}}} % arrow\)

\( \newcommand{\vectorB}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\( \newcommand{\vectorC}[1]{\textbf{#1}} \)

\( \newcommand{\vectorD}[1]{\overrightarrow{#1}} \)

\( \newcommand{\vectorDt}[1]{\overrightarrow{\text{#1}}} \)

\( \newcommand{\vectE}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash{\mathbf {#1}}}} \)

\( \newcommand{\vecs}[1]{\overset { \scriptstyle \rightharpoonup} {\mathbf{#1}} } \)

\(\newcommand{\longvect}{\overrightarrow}\)

\( \newcommand{\vecd}[1]{\overset{-\!-\!\rightharpoonup}{\vphantom{a}\smash {#1}}} \)

\(\newcommand{\avec}{\mathbf a}\) \(\newcommand{\bvec}{\mathbf b}\) \(\newcommand{\cvec}{\mathbf c}\) \(\newcommand{\dvec}{\mathbf d}\) \(\newcommand{\dtil}{\widetilde{\mathbf d}}\) \(\newcommand{\evec}{\mathbf e}\) \(\newcommand{\fvec}{\mathbf f}\) \(\newcommand{\nvec}{\mathbf n}\) \(\newcommand{\pvec}{\mathbf p}\) \(\newcommand{\qvec}{\mathbf q}\) \(\newcommand{\svec}{\mathbf s}\) \(\newcommand{\tvec}{\mathbf t}\) \(\newcommand{\uvec}{\mathbf u}\) \(\newcommand{\vvec}{\mathbf v}\) \(\newcommand{\wvec}{\mathbf w}\) \(\newcommand{\xvec}{\mathbf x}\) \(\newcommand{\yvec}{\mathbf y}\) \(\newcommand{\zvec}{\mathbf z}\) \(\newcommand{\rvec}{\mathbf r}\) \(\newcommand{\mvec}{\mathbf m}\) \(\newcommand{\zerovec}{\mathbf 0}\) \(\newcommand{\onevec}{\mathbf 1}\) \(\newcommand{\real}{\mathbb R}\) \(\newcommand{\twovec}[2]{\left[\begin{array}{r}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\ctwovec}[2]{\left[\begin{array}{c}#1 \\ #2 \end{array}\right]}\) \(\newcommand{\threevec}[3]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\cthreevec}[3]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \end{array}\right]}\) \(\newcommand{\fourvec}[4]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\cfourvec}[4]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \end{array}\right]}\) \(\newcommand{\fivevec}[5]{\left[\begin{array}{r}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\cfivevec}[5]{\left[\begin{array}{c}#1 \\ #2 \\ #3 \\ #4 \\ #5 \\ \end{array}\right]}\) \(\newcommand{\mattwo}[4]{\left[\begin{array}{rr}#1 \amp #2 \\ #3 \amp #4 \\ \end{array}\right]}\) \(\newcommand{\laspan}[1]{\text{Span}\{#1\}}\) \(\newcommand{\bcal}{\cal B}\) \(\newcommand{\ccal}{\cal C}\) \(\newcommand{\scal}{\cal S}\) \(\newcommand{\wcal}{\cal W}\) \(\newcommand{\ecal}{\cal E}\) \(\newcommand{\coords}[2]{\left\{#1\right\}_{#2}}\) \(\newcommand{\gray}[1]{\color{gray}{#1}}\) \(\newcommand{\lgray}[1]{\color{lightgray}{#1}}\) \(\newcommand{\rank}{\operatorname{rank}}\) \(\newcommand{\row}{\text{Row}}\) \(\newcommand{\col}{\text{Col}}\) \(\renewcommand{\row}{\text{Row}}\) \(\newcommand{\nul}{\text{Nul}}\) \(\newcommand{\var}{\text{Var}}\) \(\newcommand{\corr}{\text{corr}}\) \(\newcommand{\len}[1]{\left|#1\right|}\) \(\newcommand{\bbar}{\overline{\bvec}}\) \(\newcommand{\bhat}{\widehat{\bvec}}\) \(\newcommand{\bperp}{\bvec^\perp}\) \(\newcommand{\xhat}{\widehat{\xvec}}\) \(\newcommand{\vhat}{\widehat{\vvec}}\) \(\newcommand{\uhat}{\widehat{\uvec}}\) \(\newcommand{\what}{\widehat{\wvec}}\) \(\newcommand{\Sighat}{\widehat{\Sigma}}\) \(\newcommand{\lt}{<}\) \(\newcommand{\gt}{>}\) \(\newcommand{\amp}{&}\) \(\definecolor{fillinmathshade}{gray}{0.9}\)The following circuits are pre-tested netlists for SPICE 2g6, complete with short descriptions when necessary. (See Chapter 2’s Computer Simulation of Electric Circuits for more information on netlists in SPICE.)

Feel free to “copy” and “paste” any of the netlists to your own SPICE source file for analysis and/or modification.

My goal here is twofold: to give practical examples of SPICE netlist design to further understanding of SPICE netlist syntax, and to show how simple and compact SPICE netlists can be in analyzing simple circuits.

All output listings for these examples have been “trimmed” of extraneous information, giving you the most succinct presentation of the SPICE output as possible. I do this primarily to save space in this document. Typical SPICE outputs contain lots of headers and summary information not necessarily germane to the task at hand. So don’t be surprised when you run a simulation on your own and find that the output doesn’t exactly look like what I have shown here!

Example multiple-source DC resistor network circuit, part 1

Without a .dc card and a .print or .plot card, the output for this netlist will only display voltages for nodes 1, 2, and 3 (with reference to node 0, of course).

Netlist:

Multiple dc sources v1 1 0 dc 24 v2 3 0 dc 15 r1 1 2 10k r2 2 3 8.1k r3 2 0 4.7k .end

Output:

node voltage node voltage node voltage ( 1) 24.0000 ( 2) 9.7470 ( 3) 15.0000

voltage source currents name current v1 -1.425E-03 v2 -6.485E-04

total power dissipation 4.39E-02 watts

Example multiple-source DC resistor network circuit, part 2

By adding a .dc analysis card and specifying source V1 from 24 volts to 24 volts in 1 step (in other words, 24 volts steady), we can use the .print card analysis to print out voltages between any two points we desire. Oddly enough, when the .dc analysis option is invoked, the default voltage printouts for each node (to ground) disappears, so we end up having to explicitly specify them in the .print card to see them at all.

Netlist:

Multiple dc sources v1 1 0 v2 3 0 15 r1 1 2 10k r2 2 3 8.1k r3 2 0 4.7k .dc v1 24 24 1 .print dc v(1) v(2) v(3) v(1,2) v(2,3) .end

Output:

v1 v(1) v(2) v(3) v(1,2) v(2,3) 2.400E+01 2.400E+01 9.747E+00 1.500E+01 1.425E+01 -5.253E+00

Example RC time-constant circuit

For DC analysis, the initial conditions of any reactive component (C or L) must be specified (voltage for capacitors, current for inductors). This is provided by the last data field of each capacitor card (ic=0). To perform a DC analysis, the .tran (”transient”) analysis option must be specified, with the first data field specifying time increment in seconds, the second specifying total analysis timespan in seconds, and the “uic” telling it to “use initial conditions” when analyzing.

Netlist:

RC time delay circuit v1 1 0 dc 10 c1 1 2 47u ic=0 c2 1 2 22u ic=0 r1 2 0 3.3k .tran .05 1 uic .print tran v(1,2) .end

Output:

time v(1,2) 0.000E+00 7.701E-06 5.000E-02 1.967E+00 1.000E-01 3.551E+00 1.500E-01 4.824E+00 2.000E-01 5.844E+00 2.500E-01 6.664E+00 3.000E-01 7.322E+00 3.500E-01 7.851E+00 4.000E-01 8.274E+00 4.500E-01 8.615E+00 5.000E-01 8.888E+00 5.500E-01 9.107E+00 6.000E-01 9.283E+00 6.500E-01 9.425E+00 7.000E-01 9.538E+00 7.500E-01 9.629E+00 8.000E-01 9.702E+00 8.500E-01 9.761E+00 9.000E-01 9.808E+00 9.500E-01 9.846E+00 1.000E+00 9.877E+00

Plotting and analyzing a simple AC sinewave voltage circuit

This exercise does show the proper setup for plotting instantaneous values of a sine-wave voltage source with the .plot function (as a transient analysis). Not surprisingly, the Fourier analysis in this deck also requires the .tran (transient) analysis option to be specified over a suitable time range. The time range in this particular deck allows for a Fourier analysis with rather poor accuracy. The more cycles of the fundamental frequency that the transient analysis is performed over, the more precise the Fourier analysis will be. This is not a quirk of SPICE, but rather a basic principle of waveforms.

Netlist:

v1 1 0 sin(0 15 60 0 0) rload 1 0 10k * change tran card to the following for better Fourier precision * .tran 1m 30m .01m and include .options card: * .options itl5=30000 .tran 1m 30m .plot tran v(1) .four 60 v(1) .end

Output:

time v(1) -2.000E+01 -1.000E+01 0.000E+00 1.000E+01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 0.000E+00 . . * . . 1.000E-03 5.487E+00 . . . * . . 2.000E-03 1.025E+01 . . . * . 3.000E-03 1.350E+01 . . . . * . 4.000E-03 1.488E+01 . . . . *. 5.000E-03 1.425E+01 . . . . * . 6.000E-03 1.150E+01 . . . . * . 7.000E-03 7.184E+00 . . . * . . 8.000E-03 1.879E+00 . . . * . . 9.000E-03 -3.714E+00 . . * . . . 1.000E-02 -8.762E+00 . . * . . . 1.100E-02 -1.265E+01 . * . . . . 1.200E-02 -1.466E+01 . * . . . . 1.300E-02 -1.465E+01 . * . . . . 1.400E-02 -1.265E+01 . * . . . . 1.500E-02 -8.769E+00 . . * . . . 1.600E-02 -3.709E+00 . . * . . . 1.700E-02 1.876E+00 . . . * . . 1.800E-02 7.191E+00 . . . * . . 1.900E-02 1.149E+01 . . . . * . 2.000E-02 1.425E+01 . . . . * . 2.100E-02 1.489E+01 . . . . *. 2.200E-02 1.349E+01 . . . . * . 2.300E-02 1.026E+01 . . . * . 2.400E-02 5.491E+00 . . . * . . 2.500E-02 1.553E-03 . . * . . 2.600E-02 -5.514E+00 . . * . . . 2.700E-02 -1.022E+01 . * . . . 2.800E-02 -1.349E+01 . * . . . . 2.900E-02 -1.495E+01 . * . . . . 3.000E-02 -1.427E+01 . * . . . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

fourier components of transient response v(1) dc component = -1.885E-03 harmonic frequency fourier normalized phase normalized no (hz) component component (deg) phase (deg) 1 6.000E+01 1.494E+01 1.000000 -71.998 0.000 2 1.200E+02 1.886E-02 0.001262 -50.162 21.836 3 1.800E+02 1.346E-03 0.000090 102.674 174.671 4 2.400E+02 1.799E-02 0.001204 -10.866 61.132 5 3.000E+02 3.604E-03 0.000241 160.923 232.921 6 3.600E+02 5.642E-03 0.000378 -176.247 -104.250 7 4.200E+02 2.095E-03 0.000140 122.661 194.658 8 4.800E+02 4.574E-03 0.000306 -143.754 -71.757 9 5.400E+02 4.896E-03 0.000328 -129.418 -57.420 total harmonic distortion = 0.186350 percent

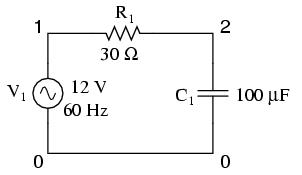

Example simple AC resistor-capacitor circuit

The .ac card specifies the points of ac analysis from 60Hz to 60Hz, at a single point. This card, of course, is a bit more useful for multi-frequency analysis, where a range of frequencies can be analyzed in steps. The .print card outputs the AC voltage between nodes 1 and 2, and the AC voltage between node 2 and ground.

Netlist:

Demo of a simple AC circuit v1 1 0 ac 12 sin r1 1 2 30 c1 2 0 100u .ac lin 1 60 60 .print ac v(1,2) v(2) .end

Output:

freq v(1,2) v(2) 6.000E+01 8.990E+00 7.949E+00

Example low-pass filter circuit

This low-pass filter blocks AC and passes DC to the Rload resistor. Typical of a filter used to suppress ripple from a rectifier circuit, it actually has a resonant frequency, technically making it a band-pass filter. However, it works well anyway to pass DC and block the high-frequency harmonics generated by the AC-to-DC rectification process. Its performance is measured with an AC source sweeping from 500 Hz to 15 kHz. If desired, the .print card can be substituted or supplemented with a .plot card to show AC voltage at node 4 graphically.

Netlist:

Lowpass filter v1 2 1 ac 24 sin v2 1 0 dc 24 rload 4 0 1k l1 2 3 100m l2 3 4 250m c1 3 0 100u .ac lin 30 500 15k .print ac v(4) .plot ac v(4) .end

freq v(4) 5.000E+02 1.935E-01 1.000E+03 3.275E-02 1.500E+03 1.057E-02 2.000E+03 4.614E-03 2.500E+03 2.402E-03 3.000E+03 1.403E-03 3.500E+03 8.884E-04 4.000E+03 5.973E-04 4.500E+03 4.206E-04 5.000E+03 3.072E-04 5.500E+03 2.311E-04 6.000E+03 1.782E-04 6.500E+03 1.403E-04 7.000E+03 1.124E-04 7.500E+03 9.141E-05 8.000E+03 7.536E-05 8.500E+03 6.285E-05 9.000E+03 5.296E-05 9.500E+03 4.504E-05 1.000E+04 3.863E-05 1.050E+04 3.337E-05 1.100E+04 2.903E-05 1.150E+04 2.541E-05 1.200E+04 2.237E-05 1.250E+04 1.979E-05 1.300E+04 1.760E-05 1.350E+04 1.571E-05 1.400E+04 1.409E-05 1.450E+04 1.268E-05 1.500E+04 1.146E-05

freq v(4) 1.000E-06 1.000E-04 1.000E-02 1.000E+00 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 5.000E+02 1.935E-01 . . . * . 1.000E+03 3.275E-02 . . . * . 1.500E+03 1.057E-02 . . * . 2.000E+03 4.614E-03 . . * . . 2.500E+03 2.402E-03 . . * . . 3.000E+03 1.403E-03 . . * . . 3.500E+03 8.884E-04 . . * . . 4.000E+03 5.973E-04 . . * . . 4.500E+03 4.206E-04 . . * . . 5.000E+03 3.072E-04 . . * . . 5.500E+03 2.311E-04 . . * . . 6.000E+03 1.782E-04 . . * . . 6.500E+03 1.403E-04 . .* . . 7.000E+03 1.124E-04 . * . . 7.500E+03 9.141E-05 . * . . 8.000E+03 7.536E-05 . *. . . 8.500E+03 6.285E-05 . *. . . 9.000E+03 5.296E-05 . * . . . 9.500E+03 4.504E-05 . * . . . 1.000E+04 3.863E-05 . * . . . 1.050E+04 3.337E-05 . * . . . 1.100E+04 2.903E-05 . * . . . 1.150E+04 2.541E-05 . * . . . 1.200E+04 2.237E-05 . * . . . 1.250E+04 1.979E-05 . * . . . 1.300E+04 1.760E-05 . * . . . 1.350E+04 1.571E-05 . * . . . 1.400E+04 1.409E-05 . * . . . 1.450E+04 1.268E-05 . * . . . 1.500E+04 1.146E-05 . * . . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Example multiple-source AC network circuit

One of the idiosyncrasies of SPICE is its inability to handle any loop in a circuit exclusively composed of series voltage sources and inductors. Therefore, the “loop” of V1-L1-L2-V2-V1 is unacceptable. To get around this, I had to insert a low-resistance resistor somewhere in that loop to break it up. Thus, we have Rbogusbetween 3 and 4 (with 1 pico-ohm of resistance), and V2 between 4 and 0. The circuit above is the original design, while the circuit below has Rbogus inserted to avoid the SPICE error.

Netlist:

Multiple ac source v1 1 0 ac 55 0 sin v2 4 0 ac 43 25 sin l1 1 2 450m c1 2 0 330u l2 2 3 150m rbogus 3 4 1e-12 .ac lin 1 30 30 .print ac v(2) .end

Output:

freq v(2) 3.000E+01 1.413E+02

Example AC phase shift demonstration circuit

The currents through each leg are indicated by the voltage drops across each respective shunt resistor (1 amp = 1 volt through 1 Ω), output by the v(1,2) and v(1,3) terms of the .print card. The phase of the currents through each leg are indicated by the phase of the voltage drops across each respective shunt resistor, output by the vp(1,2) and vp(1,3) terms in the .print card.

Netlist:

phase shift v1 1 0 ac 4 sin rshunt1 1 2 1 rshunt2 1 3 1 l1 2 0 1 r1 3 0 6.3k .ac lin 1 1000 1000 .print ac v(1,2) v(1,3) vp(1,2) vp(1,3) .end

Output:

freq v(1,2) v(1,3) vp(1,2) vp(1,3) 1.000E+03 6.366E-04 6.349E-04 -9.000E+01 0.000E+00

Example transformer circuit

SPICE understands transformers as a set of mutually coupled inductors. Thus, to simulate a transformer in SPICE, you must specify the primary and secondary windings as separate inductors, then instruct SPICE to link them together with a “k” card specifying the coupling constant. For ideal transformer simulation, the coupling constant would be unity (1). However, SPICE can’t handle this value, so we use something like 0.999 as the coupling factor.

Note that all winding inductor pairs must be coupled with their own k cards in order for the simulation to work properly. For a two-winding transformer, a single k card will suffice. For a three-winding transformer, three k cards must be specified (to link L1 with L2, L2 with L3, and L1 with L3).

The L1/L2 inductance ratio of 100:1 provides a 10:1 step-down voltage transformation ratio. With 120 volts in we should see 12 volts out of the L2 winding. The L1/L3 inductance ratio of 100:25 (4:1) provides a 2:1 step-down voltage transformation ratio, which should give us 60 volts out of the L3 winding with 120 volts in.

Netlist:

transformer v1 1 0 ac 120 sin rbogus0 1 6 1e-3 l1 6 0 100 l2 2 4 1 l3 3 5 25 k1 l1 l2 0.999 k2 l2 l3 0.999 k3 l1 l3 0.999 r1 2 4 1000 r2 3 5 1000 rbogus1 5 0 1e10 rbogus2 4 0 1e10 .ac lin 1 60 60 .print ac v(1,0) v(2,0) v(3,0) .end

Output:

freq v(1) v(2) v(3) 6.000E+01 1.200E+02 1.199E+01 5.993E+01

In this example, Rbogus0 is a very low-value resistor, serving to break up the source/inductor loop of V1/L1. Rbogus1 and Rbogus2 are very high-value resistors necessary to provide DC paths to a ground on each of the isolated circuits. Note as well that one side of the primary circuit is directly grounded. Without these ground references, SPICE will produce errors!

Example full-wave bridge rectifier circuit

Diodes, like all semiconductor components in SPICE, must be modeled so that SPICE knows all the nitty-gritty details of how they’re supposed to work. Fortunately, SPICE comes with a few generic models, and the diode is the most basic. Notice the .model card which simply specifies “d” as the generic diode model for mod1. Again, since we’re plotting the waveforms here, we need to specify all parameters of the AC source in a single card and print/plot all values using the .tran option.

Netlist:

fullwave bridge rectifier v1 1 0 sin(0 15 60 0 0) rload 1 0 10k d1 1 2 mod1 d2 0 2 mod1 d3 3 1 mod1 d4 3 0 mod1 .model mod1 d .tran .5m 25m .plot tran v(1,0) v(2,3) .end

Output:

legend: *: v(1) +: v(2,3) time v(1) (*)--------- -2.000E+01 -1.000E+01 0.000E+00 1.000E+01 2.000E+01 (+)--------- -5.000E+00 0.000E+00 5.000E+00 1.000E+01 1.500E+01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 0.000E+00 . + * . . 5.000E-04 2.806E+00 . . + . * . . 1.000E-03 5.483E+00 . . + * . . 1.500E-03 7.929E+00 . . . + * . . 2.000E-03 1.013E+01 . . . +* . 2.500E-03 1.198E+01 . . . . * + . 3.000E-03 1.338E+01 . . . . * + . 3.500E-03 1.435E+01 . . . . * +. 4.000E-03 1.476E+01 . . . . * + 4.500E-03 1.470E+01 . . . . * + 5.000E-03 1.406E+01 . . . . * + . 5.500E-03 1.299E+01 . . . . * + . 6.000E-03 1.139E+01 . . . . *+ . 6.500E-03 9.455E+00 . . . + *. . 7.000E-03 7.113E+00 . . . + * . . 7.500E-03 4.591E+00 . . +. * . . 8.000E-03 1.841E+00 . . + . * . . 8.500E-03 -9.177E-01 . . + *. . . 9.000E-03 -3.689E+00 . . *+ . . . 9.500E-03 -6.380E+00 . . * . + . . 1.000E-02 -8.784E+00 . . * . + . . 1.050E-02 -1.075E+01 . *. . .+ . 1.100E-02 -1.255E+01 . * . . . + . 1.150E-02 -1.372E+01 . * . . . + . 1.200E-02 -1.460E+01 . * . . . + 1.250E-02 -1.476E+01 .* . . . + 1.300E-02 -1.460E+01 . * . . . + 1.350E-02 -1.373E+01 . * . . . + . 1.400E-02 -1.254E+01 . * . . . + . 1.450E-02 -1.077E+01 . *. . .+ . 1.500E-02 -8.726E+00 . . * . + . . 1.550E-02 -6.293E+00 . . * . + . . 1.600E-02 -3.684E+00 . . x . . . 1.650E-02 -9.361E-01 . . + *. . . 1.700E-02 1.875E+00 . . + . * . . 1.750E-02 4.552E+00 . . +. * . . 1.800E-02 7.170E+00 . . . + * . . 1.850E-02 9.401E+00 . . . + *. . 1.900E-02 1.146E+01 . . . . *+ . 1.950E-02 1.293E+01 . . . . * + . 2.000E-02 1.414E+01 . . . . * +. 2.050E-02 1.464E+01 . . . . * + 2.100E-02 1.483E+01 . . . . * + 2.150E-02 1.430E+01 . . . . * +. 2.200E-02 1.344E+01 . . . . * + . 2.250E-02 1.195E+01 . . . . *+ . 2.300E-02 1.016E+01 . . . +* . 2.350E-02 7.917E+00 . . . + * . . 2.400E-02 5.460E+00 . . + * . . 2.450E-02 2.809E+00 . . + . * . . 2.500E-02 -8.297E-04 . + * . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Example common-base BJT transistor amplifier circuit

This analysis sweeps the input voltage (Vin) from 0 to 5 volts in 0.1 volt increments, then prints out the voltage between the collector and emitter leads of the transistor v(2,3). The transistor (Q1) is an NPN with a forward Beta of 50.

Netlist:

Common-base BJT amplifier vsupply 1 0 dc 24 vin 0 4 dc rc 1 2 800 re 3 4 100 q1 2 0 3 mod1 .model mod1 npn bf=50 .dc vin 0 5 0.1 .print dc v(2,3) .plot dc v(2,3) .end

Output:

vin v(2,3) 0.000E+00 2.400E+01 1.000E-01 2.410E+01 2.000E-01 2.420E+01 3.000E-01 2.430E+01 4.000E-01 2.440E+01 5.000E-01 2.450E+01 6.000E-01 2.460E+01 7.000E-01 2.466E+01 8.000E-01 2.439E+01 9.000E-01 2.383E+01 1.000E+00 2.317E+01 1.100E+00 2.246E+01 1.200E+00 2.174E+01 1.300E+00 2.101E+01 1.400E+00 2.026E+01 1.500E+00 1.951E+01 1.600E+00 1.876E+01 1.700E+00 1.800E+01 1.800E+00 1.724E+01 1.900E+00 1.648E+01 2.000E+00 1.572E+01 2.100E+00 1.495E+01 2.200E+00 1.418E+01 2.300E+00 1.342E+01 2.400E+00 1.265E+01 2.500E+00 1.188E+01 2.600E+00 1.110E+01 2.700E+00 1.033E+01 2.800E+00 9.560E+00 2.900E+00 8.787E+00 3.000E+00 8.014E+00 3.100E+00 7.240E+00 3.200E+00 6.465E+00 3.300E+00 5.691E+00 3.400E+00 4.915E+00 3.500E+00 4.140E+00 3.600E+00 3.364E+00 3.700E+00 2.588E+00 3.800E+00 1.811E+00 3.900E+00 1.034E+00 4.000E+00 2.587E-01 4.100E+00 9.744E-02 4.200E+00 7.815E-02 4.300E+00 6.806E-02 4.400E+00 6.141E-02 4.500E+00 5.657E-02 4.600E+00 5.281E-02 4.700E+00 4.981E-02 4.800E+00 4.734E-02 4.900E+00 4.525E-02 5.000E+00 4.346E-02

vin v(2,3) 0.000E+00 1.000E+01 2.000E+01 3.000E+01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 2.400E+01 . . . * . 1.000E-01 2.410E+01 . . . * . 2.000E-01 2.420E+01 . . . * . 3.000E-01 2.430E+01 . . . * . 4.000E-01 2.440E+01 . . . * . 5.000E-01 2.450E+01 . . . * . 6.000E-01 2.460E+01 . . . * . 7.000E-01 2.466E+01 . . . * . 8.000E-01 2.439E+01 . . . * . 9.000E-01 2.383E+01 . . . * . 1.000E+00 2.317E+01 . . . * . 1.100E+00 2.246E+01 . . . * . 1.200E+00 2.174E+01 . . . * . 1.300E+00 2.101E+01 . . .* . 1.400E+00 2.026E+01 . . * . 1.500E+00 1.951E+01 . . *. . 1.600E+00 1.876E+01 . . * . . 1.700E+00 1.800E+01 . . * . . 1.800E+00 1.724E+01 . . * . . 1.900E+00 1.648E+01 . . * . . 2.000E+00 1.572E+01 . . * . . 2.100E+00 1.495E+01 . . * . . 2.200E+00 1.418E+01 . . * . . 2.300E+00 1.342E+01 . . * . . 2.400E+00 1.265E+01 . . * . . 2.500E+00 1.188E+01 . . * . . 2.600E+00 1.110E+01 . . * . . 2.700E+00 1.033E+01 . * . . 2.800E+00 9.560E+00 . *. . . 2.900E+00 8.787E+00 . * . . . 3.000E+00 8.014E+00 . * . . . 3.100E+00 7.240E+00 . * . . . 3.200E+00 6.465E+00 . * . . . 3.300E+00 5.691E+00 . * . . . 3.400E+00 4.915E+00 . * . . . 3.500E+00 4.140E+00 . * . . . 3.600E+00 3.364E+00 . * . . . 3.700E+00 2.588E+00 . * . . . 3.800E+00 1.811E+00 . * . . . 3.900E+00 1.034E+00 .* . . . 4.000E+00 2.587E-01 * . . . 4.100E+00 9.744E-02 * . . . 4.200E+00 7.815E-02 * . . . 4.300E+00 6.806E-02 * . . . 4.400E+00 6.141E-02 * . . . 4.500E+00 5.657E-02 * . . . 4.600E+00 5.281E-02 * . . . 4.700E+00 4.981E-02 * . . . 4.800E+00 4.734E-02 * . . . 4.900E+00 4.525E-02 * . . . 5.000E+00 4.346E-02 * . . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

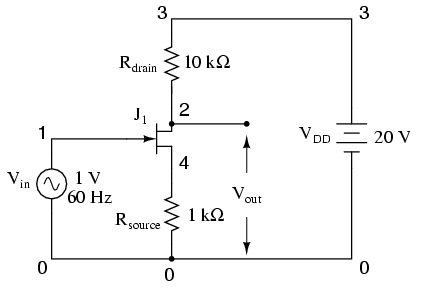

Example common-source JFET amplifier circuit with self-bias

Netlist:

common source jfet amplifier vin 1 0 sin(0 1 60 0 0) vdd 3 0 dc 20 rdrain 3 2 10k rsource 4 0 1k j1 2 1 4 mod1 .model mod1 njf .tran 1m 30m .plot tran v(2,0) v(1,0) .end

Output:

legend: *: v(2) +: v(1) time v(2) (*)--------- 1.400E+01 1.600E+01 1.800E+01 2.000E+01 2.200E+01 (+)--------- -1.000E+00 -5.000E-01 0.000E+00 5.000E-01 1.000E+00 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 1.708E+01 . . * + . . 1.000E-03 1.609E+01 . .* . + . . 2.000E-03 1.516E+01 . * . . . + . 3.000E-03 1.448E+01 . * . . . + . 4.000E-03 1.419E+01 .* . . . + 5.000E-03 1.432E+01 . * . . . +. 6.000E-03 1.490E+01 . * . . . + . 7.000E-03 1.577E+01 . * . . +. . 8.000E-03 1.676E+01 . . * . + . . 9.000E-03 1.768E+01 . . + *. . . 1.000E-02 1.841E+01 . + . . * . . 1.100E-02 1.890E+01 . + . . * . . 1.200E-02 1.912E+01 .+ . . * . . 1.300E-02 1.912E+01 .+ . . * . . 1.400E-02 1.890E+01 . + . . * . . 1.500E-02 1.842E+01 . + . . * . . 1.600E-02 1.768E+01 . . + *. . . 1.700E-02 1.676E+01 . . * . + . . 1.800E-02 1.577E+01 . * . . +. . 1.900E-02 1.491E+01 . * . . . + . 2.000E-02 1.432E+01 . * . . . +. 2.100E-02 1.419E+01 .* . . . + 2.200E-02 1.449E+01 . * . . . + . 2.300E-02 1.516E+01 . * . . . + . 2.400E-02 1.609E+01 . .* . + . . 2.500E-02 1.708E+01 . . * + . . 2.600E-02 1.796E+01 . . + * . . 2.700E-02 1.861E+01 . + . . * . . 2.800E-02 1.900E+01 . + . . * . . 2.900E-02 1.916E+01 + . . * . . 3.000E-02 1.908E+01 .+ . . * . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Example inverting op-amp circuit

To simulate an ideal operational amplifier in SPICE, we use a voltage-dependent voltage source as a differential amplifier with extremely high gain. The “e” card sets up the dependent voltage source with four nodes, 3 and 0 for voltage output, and 1 and 0 for voltage input. No power supply is needed for the dependent voltage source, unlike a real operational amplifier. The voltage gain is set at 999,000 in this case. The input voltage source (V1) sweeps from 0 to 3.5 volts in 0.05 volt steps.

Netlist:

Inverting opamp v1 2 0 dc e 3 0 0 1 999k r1 3 1 3.29k r2 1 2 1.18k .dc v1 0 3.5 0.05 .print dc v(3,0) .end

Output:

v1 v(3) 0.000E+00 0.000E+00 5.000E-02 -1.394E-01 1.000E-01 -2.788E-01 1.500E-01 -4.182E-01 2.000E-01 -5.576E-01 2.500E-01 -6.970E-01 3.000E-01 -8.364E-01 3.500E-01 -9.758E-01 4.000E-01 -1.115E+00 4.500E-01 -1.255E+00 5.000E-01 -1.394E+00 5.500E-01 -1.533E+00 6.000E-01 -1.673E+00 6.500E-01 -1.812E+00 7.000E-01 -1.952E+00 7.500E-01 -2.091E+00 8.000E-01 -2.231E+00 8.500E-01 -2.370E+00 9.000E-01 -2.509E+00 9.500E-01 -2.649E+00 1.000E+00 -2.788E+00 1.050E+00 -2.928E+00 1.100E+00 -3.067E+00 1.150E+00 -3.206E+00 1.200E+00 -3.346E+00 1.250E+00 -3.485E+00 1.300E+00 -3.625E+00 1.350E+00 -3.764E+00 1.400E+00 -3.903E+00 1.450E+00 -4.043E+00 1.500E+00 -4.182E+00 1.550E+00 -4.322E+00 1.600E+00 -4.461E+00 1.650E+00 -4.600E+00 1.700E+00 -4.740E+00 1.750E+00 -4.879E+00 1.800E+00 -5.019E+00 1.850E+00 -5.158E+00 1.900E+00 -5.297E+00 1.950E+00 -5.437E+00 2.000E+00 -5.576E+00 2.050E+00 -5.716E+00 2.100E+00 -5.855E+00 2.150E+00 -5.994E+00 2.200E+00 -6.134E+00 2.250E+00 -6.273E+00 2.300E+00 -6.413E+00 2.350E+00 -6.552E+00 2.400E+00 -6.692E+00 2.450E+00 -6.831E+00 2.500E+00 -6.970E+00 2.550E+00 -7.110E+00 2.600E+00 -7.249E+00 2.650E+00 -7.389E+00 2.700E+00 -7.528E+00 2.750E+00 -7.667E+00 2.800E+00 -7.807E+00 2.850E+00 -7.946E+00 2.900E+00 -8.086E+00 2.950E+00 -8.225E+00 3.000E+00 -8.364E+00 3.050E+00 -8.504E+00 3.100E+00 -8.643E+00 3.150E+00 -8.783E+00 3.200E+00 -8.922E+00 3.250E+00 -9.061E+00 3.300E+00 -9.201E+00 3.350E+00 -9.340E+00 3.400E+00 -9.480E+00 3.450E+00 -9.619E+00 3.500E+00 -9.758E+00

Example noninverting op-amp circuit

Another example of a SPICE quirk: since the dependent voltage source “e” isn’t considered a load to voltage source V1, SPICE interprets V1 to be open-circuited and will refuse to analyze it. The fix is to connect Rbogus in parallel with V1 to act as a DC load. Being directly connected across V1, the resistance of Rbogus is not crucial to the operation of the circuit, so 10 kΩ will work fine. I decided not to sweep the V1input voltage at all in this circuit for the sake of keeping the netlist and output listing simple.

Netlist:

noninverting opamp v1 2 0 dc 5 rbogus 2 0 10k e 3 0 2 1 999k r1 3 1 20k r2 1 0 10k .end

Output:

node voltage node voltage node voltage ( 1) 5.0000 ( 2) 5.0000 ( 3) 15.0000

Example instrumentation amplifier circuit

Note the very high-resistance Rbogus1 and Rbogus2 resistors in the netlist (not shown in schematic for brevity) across each input voltage source, to keep SPICE from thinking V1 and V2 were open-circuited, just like the other op-amp circuit examples.

Netlist:

Instrumentation amplifier v1 1 0 rbogus1 1 0 9e12 v2 4 0 dc 5 rbogus2 4 0 9e12 e1 3 0 1 2 999k e2 6 0 4 5 999k e3 9 0 8 7 999k rload 9 0 10k r1 2 3 10k rgain 2 5 10k r2 5 6 10k r3 3 7 10k r4 7 9 10k r5 6 8 10k r6 8 0 10k .dc v1 0 10 1 .print dc v(9) v(3,6) .end

Output:

v1 v(9) v(3,6) 0.000E+00 1.500E+01 -1.500E+01 1.000E+00 1.200E+01 -1.200E+01 2.000E+00 9.000E+00 -9.000E+00 3.000E+00 6.000E+00 -6.000E+00 4.000E+00 3.000E+00 -3.000E+00 5.000E+00 9.955E-11 -9.956E-11 6.000E+00 -3.000E+00 3.000E+00 7.000E+00 -6.000E+00 6.000E+00 8.000E+00 -9.000E+00 9.000E+00 9.000E+00 -1.200E+01 1.200E+01 1.000E+01 -1.500E+01 1.500E+01

Example op-amp integrator circuit with sinewave input

Netlist:

Integrator with sinewave input vin 1 0 sin (0 15 60 0 0) r1 1 2 10k c1 2 3 150u ic=0 e 3 0 0 2 999k .tran 1m 30m uic .plot tran v(1,0) v(3,0) .end

Output:

legend: *: v(1) +: v(3) time v(1) (*)-------- -2.000E+01 -1.000E+01 0.000E+00 1.000E+01 (+)-------- -6.000E-02 -4.000E-02 -2.000E-02 0.000E+00 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 6.536E-08 . . * + . 1.000E-03 5.516E+00 . . . * +. . 2.000E-03 1.021E+01 . . . + * . 3.000E-03 1.350E+01 . . . + . * . 4.000E-03 1.495E+01 . . + . . *. 5.000E-03 1.418E+01 . . + . . * . 6.000E-03 1.150E+01 . + . . . * . 7.000E-03 7.214E+00 . + . . * . . 8.000E-03 1.867E+00 .+ . . * . . 9.000E-03 -3.709E+00 . + . * . . . 1.000E-02 -8.805E+00 . + . * . . . 1.100E-02 -1.259E+01 . * + . . . 1.200E-02 -1.466E+01 . * . + . . . 1.300E-02 -1.471E+01 . * . +. . . 1.400E-02 -1.259E+01 . * . . + . . 1.500E-02 -8.774E+00 . . * . + . . 1.600E-02 -3.723E+00 . . * . +. . 1.700E-02 1.870E+00 . . . * + . 1.800E-02 7.188E+00 . . . * + . . 1.900E-02 1.154E+01 . . . + . * . 2.000E-02 1.418E+01 . . .+ . * . 2.100E-02 1.490E+01 . . + . . *. 2.200E-02 1.355E+01 . . + . . * . 2.300E-02 1.020E+01 . + . . * . 2.400E-02 5.496E+00 . + . . * . . 2.500E-02 -1.486E-03 .+ . * . . 2.600E-02 -5.489E+00 . + . * . . . 2.700E-02 -1.021E+01 . + * . . . 2.800E-02 -1.355E+01 . * . + . . . 2.900E-02 -1.488E+01 . * . + . . . 3.000E-02 -1.427E+01 . * . .+ . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Example op-amp integrator circuit with squarewave input

Netlist:

Integrator with squarewave input vin 1 0 pulse (-1 1 0 0 0 10m 20m) r1 1 2 1k c1 2 3 150u ic=0 e 3 0 0 2 999k .tran 1m 50m uic .plot tran v(1,0) v(3,0) .end

Output:

<(1) +: v(3) time v(1) (*)————-1.000E+00 -5.000E-01 0.000E+00 5.000E-01 1.000E+00 (+)————-1.000E-01 -5.000E-02 0.000E+00 5.000E-02 1.000E-01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 -1.000E+00 * . + . . 1.000E-03 1.000E+00 . . + . * 2.000E-03 1.000E+00 . . + . . * 3.000E-03 1.000E+00 . . + . . * 4.000E-03 1.000E+00 . . + . . * 5.000E-03 1.000E+00 . . + . . * 6.000E-03 1.000E+00 . . + . . * 7.000E-03 1.000E+00 . . + . . * 8.000E-03 1.000E+00 . .+ . . * 9.000E-03 1.000E+00 . +. . . * 1.000E-02 1.000E+00 . + . . . * 1.100E-02 1.000E+00 . + . . . * 1.200E-02 -1.000E+00 * + . . . . 1.300E-02 -1.000E+00 * + . . . . 1.400E-02 -1.000E+00 * +. . . . 1.500E-02 -1.000E+00 * .+ . . . 1.600E-02 -1.000E+00 * . + . . . 1.700E-02 -1.000E+00 * . + . . . 1.800E-02 -1.000E+00 * . + . . . 1.900E-02 -1.000E+00 * . + . . . 2.000E-02 -1.000E+00 * . + . . . 2.100E-02 1.000E+00 . . + . . * 2.200E-02 1.000E+00 . . + . . * 2.300E-02 1.000E+00 . . + . . * 2.400E-02 1.000E+00 . . + . . * 2.500E-02 1.000E+00 . . + . . * 2.600E-02 1.000E+00 . .+ . . * 2.700E-02 1.000E+00 . +. . . * 2.800E-02 1.000E+00 . + . . . * 2.900E-02 1.000E+00 . + . . . * 3.000E-02 1.000E+00 . + . . . * 3.100E-02 1.000E+00 . + . . . * 3.200E-02 -1.000E+00 * + . . . . 3.300E-02 -1.000E+00 * + . . . . 3.400E-02 -1.000E+00 * + . . . . 3.500E-02 -1.000E+00 * + . . . . 3.600E-02 -1.000E+00 * +. . . . 3.700E-02 -1.000E+00 * .+ . . . 3.800E-02 -1.000E+00 * . + . . . 3.900E-02 -1.000E+00 * . + . . . 4.000E-02 -1.000E+00 * . + . . . 4.100E-02 1.000E+00 . . + . . * 4.200E-02 1.000E+00 . . + . . * 4.300E-02 1.000E+00 . . + . . * 4.400E-02 1.000E+00 . .+ . . * 4.500E-02 1.000E+00 . +. . . * 4.600E-02 1.000E+00 . + . . . * 4.700E-02 1.000E+00 . + . . . * 4.800E-02 1.000E+00 . + . . . * 4.900E-02 1.000E+00 . + . . . * 5.000E-02 1.000E+00 + . . . * - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -